Technology Roadmap

Technology Roadmap

Technology Roadmap

Silicon-Photonics PCM Heterogeneous Integration + Crossbar Photonic Matrix

Product Center

Product Center

Product Center

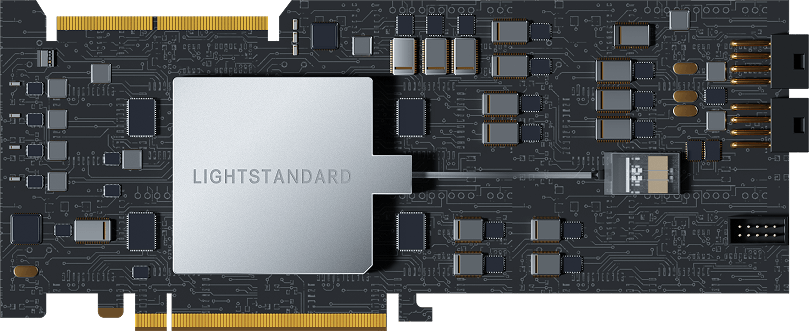

Photonic in-memory computing chip combined with mixed-signal SoC, utilizing photonic-electronic hybrid architecture and 3D co-packaging. Features built-in optical interconnect, high integration, stability, and low power. Enables flexible multi-node systems with native FP8 support.

Next-gen all-optical large-scale AI computing system with integrated photonic-electronic cards/modules/clusters. Pioneers photonic-electronic computing architecture, delivering full-scenario, full-stack optical solutions via optical computing, interconnect, and transmission.

Technology Roadmap

Technology Roadmap

Technology Roadmap

Development History

Development History

Development History

News & Updates

News & Updates

News & Updates